VCS常用操作

VCS常用操作

主要参考:

1、VCS User Guide 2020

2、知乎专栏

1 VCS简介

VCS全称为 verilog compiled simulator ,是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。 VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。

vcs用于编译Verilog/SystemVerilog、生成仿真波形、覆盖率等。

仿真波形有VCD+和fsdb( Fast Signal DataBase )两种,其中fsdb需要结合Verdi产生及使用。

VCS_MX为mixed hdl仿真器,支持vhdl+verilog+sv的混合仿真。vcs则是纯verilog的。当然,目前vcs也是有sv支持的。它们在feature上唯一的区别在于对vhdl的支持。

当然,如果没有vhdl的设计或者验证还是VCS好些,速度略好。

2 VCS Flow

VCS有两种flow,两步式(Two-step Flow )和三步式(Three-step Flow)。平时两步式用的多。

1)两步式:

只适用于Verilog/sv,包括编译、仿真两个流程。

- 编译:

编译生成二进制可执行文件simv(可用编译指定name,一般不会改name),用于第二步的仿真。

编译又有debug mode和optimized mode两种模式(也对应叫作Interactive mode和Batch mode)。debug mode适用于开发周期中使用,optimized mode适用于回归时使用,这是vcs会给出最优的编译时间。

编译指令: vcs [compile options] Verilog_files

具体编译参数介绍:(vcs -h),详见编译章节。

- 仿真:

对应编译的两种模式(debug/optimized),仿真时又对应有交互模式(Interactive mode)和批处理模式(Batch mode)。

Interactive mode仿真:仿真可以使用VCS的GUI(DVE)、Verdi、统一命令行接口(UCLI)三种。编译时需要加选项: -debug_access(+<option>)

Batch mode仿真:仿真指令是 simv

仿真设计命令: executable [runtime_options]

-gui:启动Verdi(前提是设置了环境变量VERDI_HOME)-ucli:用UCLI模式启动simv仿真

还有其他参数,可以看userguide,也可在网上找找看。

2)三步式

三步式包括分析(Analysis)、细化(Elaboration)和仿真(Simulation)三个流程,分析+细化=编译?。

- 分析:

分析过程会检查语法错误,并生成中间件文件用于评估过程。

- 细化:

编译生成二进制可执行文件simv用于第三步的仿真。

- 仿真:

同两步式

3 VCS编译

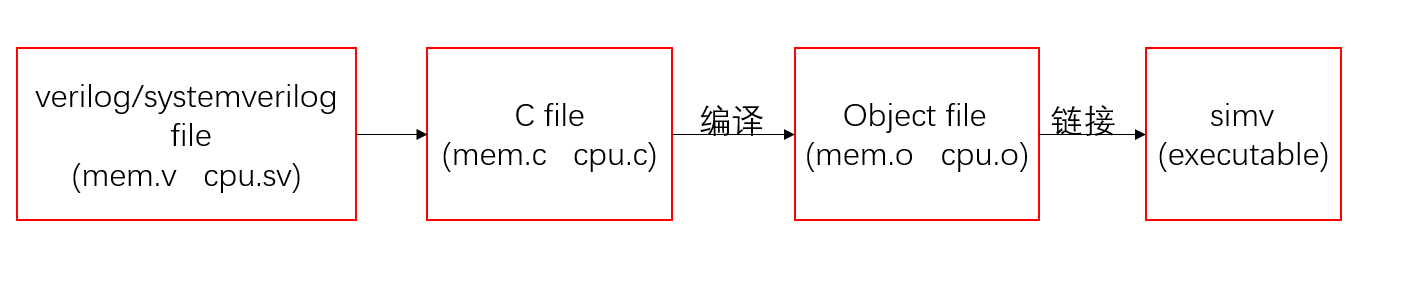

编译过程: VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。

第一步sv到c的过程是怎么做的?

编译:c到o是将多个c语言编译成汇编代码, 汇编器会将汇编代码翻译成机器码,也就是将汇编代码转换成CPU可以直接执行的指令。汇编器的输出是一个目标文件,包含了可执行代码和数据,但还不能直接运行。

链接:链接器会将多个目标文件合并成一个可执行文件,它会将所有的函数和数据段放到一个地址空间中,并解析函数之间的调用关系,使得程序可以正确地执行。

1)编译命令

编译的基本指令是:vcs [compile options] verilog_files

VCS编译命令中+ -区别-:一般是编译时用的,编译工具自带的。+:是插件,环境,验证语言,等等加的,可扩展的,自定义的。

| options | 解释 | 备注 |

|---|---|---|

| -R | 编译后立即运行,即编译完成后立即执行 ./simv | |

| -Mupdate | 源文件有修改时,只重新编译有改动的.v文件,节约编译时间。 | Modify update |

| -sverilog | 打开对Systemverilog的支持,编译Systemverilog文件时使用。 | |

| -timescale=1ns/1ns | 设置仿真精度 | 全局,大于sv文件内的? |

| -o simv_file | 编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。 | |

| -f filelist.f | 编译文件列表 | |

| -gui | 仿真时打开DVE gui界面 | |

| -verdi | 使用verdi图形界面 | |

| -l filename | 编译时产生的Log信息写到文件filename中 | |

| -ntb_opts $(UVM_VER) | 指定本次编译的UVM库,这里是用的是VCS安装自带库 | |

| -full64 | 匹配64位服务器系统 | |

| -debug_all | 打开debug开关,使能UCLI命令行 | |

| -fsdb | 仿真过程同时生成 fsdb格式的波形 | |

| +v2k | 支持verilog2001标准 | version 2k? |

| +libext+extension+ | 拓展文件,e.g. +libext+a.v+b.v+,添加a.v和b.v库文件添加到编译。 | |

| +incdir+directory+ | include文件,e.g. +incdir+dirA+dirB+,把dirA和dirB加入include搜索路径。 | |

| +define+VCS | 定义全局的VCS,编译器在编译时如果源文件有类似`ifdef VCS等字样,那么会执行定义之后的代码。 | 常用 |

暂不涉及覆盖率统计。

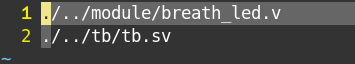

2)filelist.f

filelist.f这个文件是sv文件的列表,列出所需参与编译的sv文件名。编译时给出filelist.f文件即可。

使用命令find -name *.sv > filelist.f可以将所有sv文件名写入filelist.f中 。

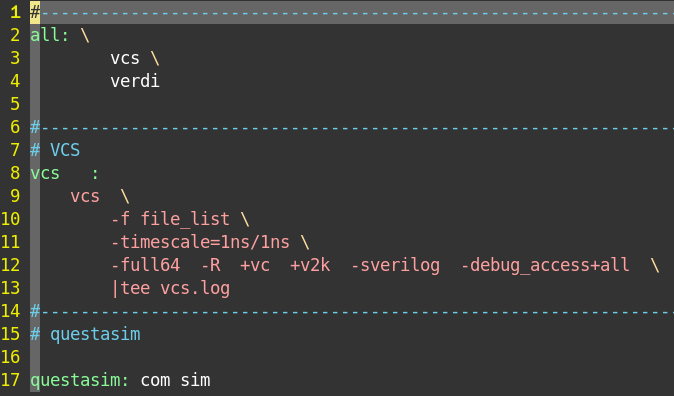

3)Makefile

VCS的编译时开关选项很多,所以借助Makefile进行编译。Makefile的指令是make [target],其中target是我们自己设定的,每个target对应一条编译指令,默认是执行第一个target。

格式:target首行对齐,后跟“:”,后可跟其他target。命令换行后输入,需要一个tab对齐,命令太长使用“\”分行。也会使用一些环境变量,如${UVM_HOME}。

示例:如图,make all执行等于执行make vcs verdi,make vcs等于执行vcs -f file_list -timescale=1ns/1ns ...

给出模板:

1 | #------------------------------------------------------------------------------------------------------- |

4)

4 VCS仿真

编译或进行仿真,主要看具体的波形,debug。

仿真基本指令: executable [runtime_options]

1)仿真

| 仿真开关: | 作用: |

|---|---|

| -s | 什么时候结束仿真 |

| +userswitch | $plusargs() switches,接收一些参数 |

| -E echo | |

| -I logfile | 仿真信息写到logfile中 |

| -gui | 仿真时打开DVE gui界面(user guide说在设置verdi环境变量后是打开verdi的) |

| ./simv -gui & | 后台执行,不要把当前界面锁住。 第一行数字是进程号。 |

2)debug

暂未学习

5 实例

VCS+Verdi

需重新整理,笔记太乱